製品

RTLコード検証サービス 「RTL Valid™」

FPGAやSoCデバイスの設計において、RTLコードの品質を確保することは極めて重要です。設計の初期段階で潜在的な問題を検出し迅速に対応することが、開発の成功を左右する決定的なポイントとなります。

OKIアイディエスでは、FPGA設計における長年の豊富な開発経験を活かし、LINT検証、Formal検証、CDC検証を活用したRTLコード検証サービス「RTL Valid™」をご提供しています。

これらの検証により、RTLコードの高品質化を実現し、お客様の設計課題の解決に貢献します。

■設計現場が直面する課題とは?

最近のFPGAやSoCデバイスの開発においては、RTLコード設計の複雑化に伴い、問題解決の難易度がさらに高まっています。このような状況下で、検出できるはずのコード不良が見落とされると、以下のような課題に直面する可能性があります。

- 意図した通りに機能が正常に動作しない

- 未定義動作や信号不整合の放置により手戻りが多発する

- 高速データ転送でエラーが発生する

- シミュレーションや機能検証で意図しない結果が生じ、デバッグに多大な時間を要する

- RTLコードの可読性が低く、保守や設計変更が困難となる

これらの課題を見過ごしたまま開発を進めてしまうと、後々大きな追加コストや開発遅延につながる可能性があります!

■課題を放置した場合に考えうるリスク

- 検証工程で致命的な不具合が検出され、大幅な手戻りが発生する

- 量産段階でテストが不合格となり、市場投入が遅延する

- 設計の脆弱性が市場に流出し、高額なサポート費用が発生する

- 製品の信頼性低下によるユーザー離れや、市場での競争力の低下を招く

これらのリスクを未然に防ぐためには、開発の初期段階で問題にアプローチすることが極めて重要です!

「RTL Valid™」はRTLコード設計を分析・検証するための静的解析ソリューションです。

以下の特長をいかし、設計プロセスにおける品質を確保します。

LINT検証

- 設計ルールに基づき、コードの文法違反や構文ミスを解析

- 見落としがちな設計上の問題を網羅的に検出

Formal検証

- テストベンチ不要でRTLに混入しやすいバグを自動検出

- シミュレーションでは検出が困難な問題も検出可能

CDC検証

- 異なるクロックドメイン間での信号遷移リスクを正確に解析

- データ損失や同期エラーを未然に防止

- ※CDC:クロックドメインクロッシング (Clock Domain Crossing)の略。 複数のクロック信号を持つデザインの整合説を保つ重要な概念です。

- 早期問題発見と手戻り削減

: SIM(シミュレーション)検証の前段階で潜在的なエラーを特定し、修正期間を大幅に短縮 - 信頼性の高い製品設計

: 問題の解消により製品の品質向上を実現 - 設計プロセスの効率化

: 時間を要するデバッグ工程を大幅に短縮し、市場投入スピードを加速

RTLコード設計の品質を担保する2つのポイント

設計品質を確保し、課題解決を成功に導くためには、以下の2つのステップが必要です。

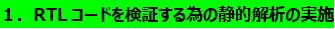

- RTLコードを検証するための静的解析の実施

- 静的解析を開発フローの2つの工程で実施

RTLコードの品質を確保するためには、静的解析ツールの活用が鍵となります。

特に、LINT検証ツール、Formal検証ツール、CDC検証ツールは、潜在的な問題の検出や品質確保に不可欠です。

①LINT検証ツール:文法や構文のチェック

- 文法エラーの検出

:コード文法の誤りや未初期化変数を検出し、構文ミスを早期に修正。 - コーディング規約の確認

:特定のコーディングスタイルに従っているかをチェック - 潜在的なバグの指摘

:見逃されがちな論理的な誤りや、潜在的な問題個所を特定。設計初期段階で修正が可能 - 保守性の向上

:曖昧なスタイルや非推奨の構文使用を指摘し、コードの一貫性と可読性を改善

②Formal検証ツール:設計したRTLデザインに潜む不安定要素や非効率性をチェック

- デッドコードの検出

:実行されることがない不要なコードを検出 - 非遷移信号の検出

:一定の論理値のまま固定され、トグルしない信号を検出 - デッドロック回路の検出

:ステートマシンが意図しない固定状態に陥り、正常な動作から脱落する可能性を検出 - 不定値伝播の検出

:初期化不良や未定義値の代入により、不定値が回路全体に広がる問題を検出

③CDC検証ツール:クロック領域間の信号転送に特化した問題を検出

- クロック同期の確認

:異なるクロックドメイン間で信号が適切に同期されているかを確認し、データ破損のリスクを防止 - メタステーブル状態の検出

:クロックドメイン間で不適切なタイミングで信号がサンプリングされることで発生する、不安定なメタステーブル状態に陥るリスクを早期に検出 - 設計の整合性向上

:クロックドメインをまたぐ設計の正確性を確保し、デザイン全体の整合性と品質を向上 - 潜在的リスクの早期発見

:通常のシミュレーションでは検出が難しいクロックドメイン間のタイミング問題を迅速に特定し、手戻りを防ぐ

ヒューマンチェックやレビューでは見つけにくい問題の実例 ○の問題検出が可能

各単体検証では、下記の問題全てを検出することはできません。

LINT検証、Formal検証、CDC検証を全て実施することで、これらの問題を網羅的に検出することが可能になります。

| No | 問題 | LINT 検証 |

Formal 検証 |

CDC 検証 |

備考 |

|---|---|---|---|---|---|

| 1 | コーディング規約違反 | ○ | × | × | コーディングスタイルや慣習の違反を特定 |

| 2 | 異クロックドメイン間の信号遷移 | × | × | ○ | クロックドメイン境界を越える信号の問題を検出 |

| 3 | 未使用信号の検出 | ○ | ○ | × | 使用しない信号をリソース節約の観点から指摘 |

| 4 | メタステーブル状態のリスク | × | × | ○ | シンクロナイザを利用していない箇所でメタステーブルの可能性を検出 |

| 5 | ポート接続ミス | ○ | ○ | × | 信号の接続が誤っていることや欠落をチェック |

| 6 | リセットやイネーブル信号の同期性 | ○ | × | ○ | コードスタイル、同期性自体を検証 |

| 7 | ビット幅の不整合 | ○ | ○ | × | ポートや内部信号のビット幅の一致を確認 |

| 8 | デッドコード | × | ○ | × | 実行されることがない不要なコードを検出 |

| 9 | トグルしない信号 | × | ○ | × | 値が変化しない信号や未使用の信号を特定 |

| 10 | ステートマシンのデッドロック | × | ○ | × | 状態遷移が進行不能となる箇所や未定義の状態を特定 |

| 11 | 不定値の伝播 | × | ○ | × | 初期化不良や未定義値により発生した不定値(X値)が回路内で伝播する問題を特定 |

静的解析を開発フローの2つの工程で実施することで、RTLコードの品質を効果的に向上させ、設計プロセス全体の効率化を実現します。当社のFPGA開発フローでは、以下の2段階で静的解析を行います。

当社のFPGA開発フローをご紹介します。

・第1段階:RTLコード設計後の静的解析1

上記FPGA開発フローにおける開発フロー2 「RTLコード設計」の後に、「静的解析1」を実施します。

この段階では、LINT検証、Formal検証、CDC検証を通じて、以下のような重要な指摘事項や潜在的な問題を洗い出し、解決します。

- 文法エラーやコーディング規約違反の特定

- デッドコードやデッドロックの検出

- クロック領域間の同期問題の検出

- 未初期化変数や使用不可パターンの修正案提示

この段階で問題を早期に解決することで、設計の基盤を強化し、後工程での手戻りリスクを大幅に低減します。

・第2段階:論理合成前の静的解析2

上記FPGA開発フローにおける開発フロー8 「論理合成」の前に、「静的解析2」を実施します。

設計が意図する通りに機能することをSIM検証で確認しますが、そこで不具合を検出した場合は、RTLコードの修正が必要になります。このとき、修正したコードにも問題が含まれる可能性があるため、論理合成に進む前に必ず静的解析を実施します。

静的解析2を実施したコードのみを「論理合成」へ進めることで、最終的なRTLコードの品質を確保します。

RTLコード検証サービス「RTL Valid™」のサービス内容

「RTL Valid™」は、LINT検証、Formal検証、CDC検証を、お客様の必要性に応じた組み合わせでご提供します。

ここでは、各検証の実施する内容やOUTPUT(成果物)をご紹介します。

・LINT検証

LINT検証では、RTLコードの設計規則やスタイルに基づく静的解析を行い、コード品質の向上を目指します。

以下の手順により実施します。

| 検証STEP | 実施内容 | OUTPUT | 備考 |

|---|---|---|---|

| 1 | LINTチェックを掛けて、 Rule/Recommendation1/2/3抽出 |

ツール診断 レポート |

検証ツールを使用 |

| 2 | Rule/Recom内容の解析と整理 | 解析レポート | 診断レポートの結果を基に実施 |

| Rule/Recom箇所の特定と指定 | |||

| 各Rule/Recom内容の説明 | |||

| 3 | 各Rule/Recom内容に 対しての修正方法の立案 |

修正案レポート | 解析レポートの結果を基に実施 |

| 4 (Option) |

各Rule内/Recom内容に対して修正を実施 LINTチェックで、指摘事項に問題が無いことを確認 |

修正後RTL 解析レポート |

修正案レポートの結果を基に実施 |

使用検証ツール:ALDEC社製ALINT-PRO™

・Formal検証

Formal検証では、RTLコードに潜む機能的な誤りや不安定要素をチェックします。

以下の手順により実施します。

| 検証STEP | 実施内容 | OUTPUT | 備考 |

|---|---|---|---|

| 1 | AutoCheckを実行し、 Violations/Cautions/Information抽出 |

ツール診断 レポート |

検証ツールを使用 |

| 2 | V/C/I内容の解析と整理 | 解析レポート | 診断レポートの結果を基に実施 |

| V/C/I箇所の特定と指定 | |||

| V/C/I内容の説明 | |||

| 3 | 各V/C内容に対しての修正方法の立案 | 修正案レポート | 解析レポートの結果を基に実施 |

| 4 (Option) |

各V/C内容に対して修正を実施 AutoCheckで、指摘事項に問題が無いことを確認 |

修正後RTL 解析レポート |

修正案レポートの結果を基に実施 |

使用検証ツール:シーメンスEDA社製Questa®-AutoCheck

・CDC検証

CDC検証では、クロック領域間の信号転送に特化した静的解析を行い、リスクの早期発見を目指します。

以下の手順により実施されます。

| 検証STEP | 実施内容 | OUTPUT | 備考 |

|---|---|---|---|

| 1 | CDCチェックを掛けて、 Violations/Cautions/Evaluations抽出 |

ツール診断 レポート |

検証ツールを使用 |

| 2 | V/C/E内容の解析と整理 | 解析レポート | 診断レポートの結果を基に実施 |

| V/C/E箇所の特定と指定 | |||

| V/C/E内容の説明 | |||

| 3 | 各V/C/E内容に対しての修正方法の立案 | 修正案レポート | 解析レポートの結果を基に実施 |

| 4 (Option) |

各V/C/E内容に対して修正を実施 CDCチェックで、指摘事項に問題無き事を確認 |

修正後RTL 解析レポート |

修正案レポートの結果を基に実施 |

使用検証ツール:シーメンスEDA社製Questa®-CDC

RTLコード検証サービス「RTL Valid™」の特長

「RTL Valid™」は、単なるツールの利用にとどまらず、経験と専門知識を活かした実効性の高いプロセスを通じて、お客様の設計品質を向上させます。その特長をご紹介します。

- 検証ツールの効果的な利用と適切な設定

LINT検証、Formal検証およびCDC検証を効果的に行うためには、プロジェクトごとに最適なツールの設定が必要です。当社の熟練したエキスパートが高度な設定を行い、効果的な検証を実現します。 - 指摘事項の正確な理解と適切な修正方法の提案

検証ツールが出力する指摘事項(Description)は、専門用語や複雑な英文表現を含むことが多く、誤解を招く可能性があります。当社は指摘事項を正確に解釈し、設計要件に応じた的確な修正方法をお客様へ提案することで、品質改善を効果的にサポートします。 - 経験に基づいた実践的アプローチ

ただツールを使用するだけでは、効果的な検証は実現しません。当社のエキスパートは、多様な業界で培った豊富な経験と専門的な知識をいかし、お客様のニーズに応じた実効性の高い検証プロセスを構築し、課題を解決します。

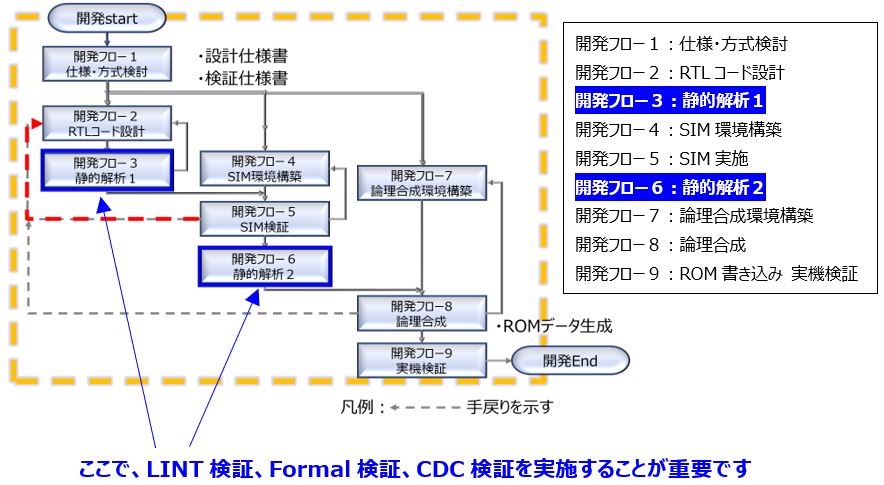

【LINT検証レポートの一例】

RTLコード検証サービス「RTL Valid™」が選ばれる理由

- 専門知識×ツール活用の融合

熟練したエキスパートが、専門知識を活かしてツールを最大限に活用。お客様の設計品質向上を実現します。 - 的確な修正案の提示

問題を正確に分析し、効果的で具体的な修正案を提示。お客様の設計品質向上を強力にサポートします。 - 広範な業界経験と実績

さまざまな業界での設計で培った豊富なノウハウを活かし、お客様に最適な検証プロセスをご提供します。

設計品質への不安や、品質不良にお困りの方、また静的解析の導入を検討されている方

↓↓↓↓↓

RTLコードの設計品質を向上させるために、ぜひ私たちにお任せください!

当社のエキスパートが、的確な修正方法をご提案いたします。

お気軽にお問い合わせください。

- リーフレット

RTLコード検証サービス[1.1MB]

本ページ記載のサービスに関するご質問、ご相談がございましたら、お気軽にお問い合わせください。

- お問い合わせ

- お問い合わせフォームはこちら

メルマガで最新情報、当社主催のWebセミナー情報を配信しております。お役に立てるよう配信してまいりますので、是非ご登録お願いいたします。

- ※記載されている会社名、製品名は、各社の商標または登録商標です。

- ※ここに記載されている仕様、デザインなどは予告なしに変更する場合があります。