Tech Blog

今さら聞けないFPGAとは

小野です!

よろしくお願いします!!

よろしくお願いします!!

こんにちは、小野です。

今回は初心に帰って、『FPGA』とはどんなものなのかについて紹介していきます。

このブログって当たり前に『FPGA』って出てきますよね。

OKIアイディエスは、その筋では『FPGA』の開発で一目置かれていますよね。ただ、『FPGA』というデバイスを知らない人もいるかもしれませんね。

最近はいろいろな分野の新たな読者が増えてきているので、こうした方々にも『FPGA』の魅力を伝えていきたいですね。

たまには初心に帰って、今回は『FPGA』とは何かについて改めて紹介していきましょう。

というか、私自身も理解していない部分もありそうなので、是非お願いしたいです。この機会にしっかり学びましょう!

FPGAとその他のデバイスの違い

では問題です。『FPGA』とは何の略でしょう?

『FPGA』は「Field Programmable Gate Array」の略です。

自由に回路の設計や変更を行うことができる半導体デバイスです。

自由に回路の設計や変更を行うことができる半導体デバイスです。

正解です。世の中には他にもCPUやGPU、ASICなどのプロセッサがあります。CPUはコンピューター、スマホなど様々な機器に搭載されており、組み込まれた様々なプログラムの実行やコンポーネントを制御しながらデータ処理を行っています。

GPUは並列処理に特化しており、多数のコアを持つことで大量の画像を高速に処理できます。この特性がビッグデータの分析や仮想通貨のマイニング、AI処理などの分野で活用されています。GPUの並列処理能力は、特にディープラーニングのモデル訓練において強力なツールとなっていますよね。

よく勉強してるじゃない!

ASICはApplication Specific Integrated Circuitの略で、特定の用途に特化して設計されたデバイスです。

特定の演算処理しかできませんが、その分、処理が非常に高速で、消費電力も抑えられます。また、大量に生産することで生産コストが低く抑えられるというメリットもあります。

ASICはApplication Specific Integrated Circuitの略で、特定の用途に特化して設計されたデバイスです。

特定の演算処理しかできませんが、その分、処理が非常に高速で、消費電力も抑えられます。また、大量に生産することで生産コストが低く抑えられるというメリットもあります。

これらのデバイスと比較すると、『FPGA』はどんなメリットがあるのでしょうか?

良い質問ですね。

『FPGA』の大きなメリットは、プログラミングによって論理回路を書き換えられる柔軟性ですね。AISCではまず不可能ですが、『FPGA』なら開発完了後や製品が市場に出た後でも、論理回路を変更してアップデートすることが可能です。この特徴が、製品のライフサイクルを通じて適応力を持たせる大きなメリットとなっています。

『FPGA』の大きなメリットは、プログラミングによって論理回路を書き換えられる柔軟性ですね。AISCではまず不可能ですが、『FPGA』なら開発完了後や製品が市場に出た後でも、論理回路を変更してアップデートすることが可能です。この特徴が、製品のライフサイクルを通じて適応力を持たせる大きなメリットとなっています。

なるほど!理解が深まりました!

『FPGA』のデータ処理性能的には、どのような特徴があるんでしょうか?

『FPGA』のデータ処理性能的には、どのような特徴があるんでしょうか?

良い視点です!

CPUはプログラムの実行や制御に、GPUは大規模な演算の並列処理にそれぞれ特化しています。しかし、デバイスにやらせたい事が増えていくと、CPUやGPUへの負荷は大きくなります。その結果、何が起こるでしょう?

消費電力が増えたり、発熱量が大きくなったりする問題が生じます。

CPUはプログラムの実行や制御に、GPUは大規模な演算の並列処理にそれぞれ特化しています。しかし、デバイスにやらせたい事が増えていくと、CPUやGPUへの負荷は大きくなります。その結果、何が起こるでしょう?

消費電力が増えたり、発熱量が大きくなったりする問題が生じます。

ということは…!?

実は、消費電力に対して、データ処理性能を考えると『FPGA』の方が優れているんです。それは、『FPGA』が内部に持つメモリーが寄与しているからなんですよ。この内部メモリーのおかげで、データの処理速度が向上し、消費電力を抑えながら効率的に動作できるのです。

内部メモリー…?

具体的にそれがどう『FPGA』のデータ処理に影響を与えるのでしょう?

具体的にそれがどう『FPGA』のデータ処理に影響を与えるのでしょう?

『FPGA』にはBRAM(Block RAM)という内部メモリーが組み込まれているんです。これによって内部メモリーを効率的に確保でき、外部メモリーへの頻繁なアクセスを減少させられます。その結果、データの処理速度を上げつつも、消費電力を抑えることが可能になるんです。

なるほど、だからこそ消費電力も抑えられているんですね~。こうやって改めて整理してみると、『FPGA』のメリットは本当に多岐にわたりますね。実際、うちの案件でも、CPUでは難しい、演算処理や信号処理、インターフェース処理、データ処理などの開発で『FPGA』が活躍しているのを多く見かけます。

ですね。他にも装置の使用環境が変わって、プロトコルやインターフェースが変わったことで、『FPGA』の設計変更の対応をしてほしいというご相談もあります。

ところで、『FPGA』の回路設計ってどんなことを具体的にやっているか知ってる?

ところで、『FPGA』の回路設計ってどんなことを具体的にやっているか知ってる?

うーん、唐突に言われると…。

正直、僕には設計者の皆さんがパソコンに向かってひたすらコーディングしているイメージしかありませんね・・・

正直、僕には設計者の皆さんがパソコンに向かってひたすらコーディングしているイメージしかありませんね・・・

ひたすらコーディング…だけではないんです。

他にも検証したり、デバッグしたりと色々あるんです。

少しずつ説明するので、認識を改めてください!(笑)

他にも検証したり、デバッグしたりと色々あるんです。

少しずつ説明するので、認識を改めてください!(笑)

FPGAの設計

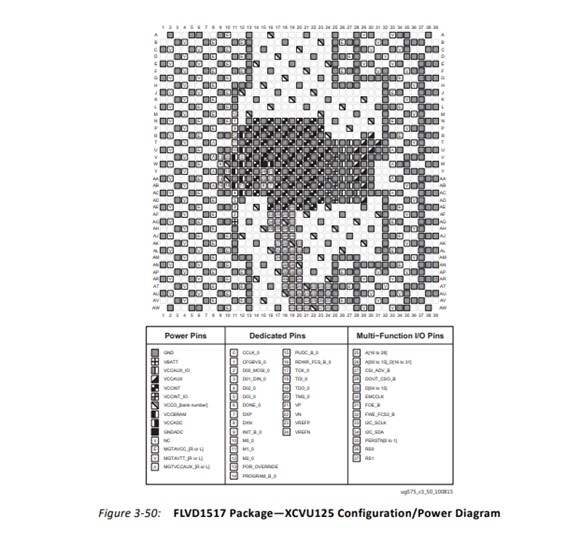

『FPGA』は多くの端子があって、これをピンと呼ぶこともあります。「このピンにつなげばこんなことができます」と、決まっているものもあれば、設計者が自身のコーディング次第で自由に機能を割り当てられる汎用ピンもあるんです。

じゃあこれをちょろっと見れば、理解して設計できるんですね。なんだ。簡単そうじゃないですか!

では、たとえばAMD社の『FPGA』のデータシートを一緒に見てみましょう。これで具体的な設計プロセスを少し体験できますよ。

えぇ!?こんなにいっぱい…。しかも、複雑ですね…。

どれがどれだか わかんなくなりそうです。

どれがどれだか わかんなくなりそうです。

それに加えて、電源などの専用ピンや特別な機能を持っているピンもあります。他にも、I/O端子、タイミング、電圧、I/Oバンク…などなど。知っておくべき要素が盛りだくさん!正直、一回で全部を説明するのは難しいから、少しづつ覚えていきましょう!

こんなにたくさんのことを考慮して設計する必要があるんですね。こうした端子に何をどう接続するのか考えながら、論理回路の設計を行っているんですね。

さっき言った代表的なものとしてI/Oスタンダードに則ったI/O端子というものがあります。これは、電子機器やコンピューターシステム間でデータを正しくやりとりするための標準規格に則った端子です。

たとえば、USB、HDMI、Ethernet、PCIe Expressなどがあります。それらの規格に対応することで、『FPGA』はさまざまなデバイスとシームレスに接続できます。

たとえば、USB、HDMI、Ethernet、PCIe Expressなどがあります。それらの規格に対応することで、『FPGA』はさまざまなデバイスとシームレスに接続できます。

他には、データシートからどんな情報がわかるんですか?

もっと『FPGA』について知りたいです!

仕様や注意点など、まだまだたくさんありそうですね。

もっと『FPGA』について知りたいです!

仕様や注意点など、まだまだたくさんありそうですね。

他にも、電圧のような電気的特性、ピンの配置と割り当て、タイミング設定など、様々な情報がデータシートには載っているんです。これらの情報を確認することで、『FPGA』を適切に使用し、最大限のパフォーマンスを引き出すことができるんです。

なるほど!さまざまな情報を基に設計していることがよくわかりました!では、この設計を実際にはどういう風に役立てるんですか?具体的な応用例とか、実際のプロジェクトでの活用についても知りたいです!

実際の設計業務はFPGAベンダーが提供しているツールを使って行います。たとえば、AMD製のFPGAを設計する場合には、「Vivado」という設計ツールを使います。このツールを使うことで、回路の配置や配線、さらにはシミュレーションやデバッグも効率的に行えるんです。

あぁ!「Vivado」という名前はよく聞きますね!

確かに設計の話ではちょくちょく出てきます。どんなことができるのか、もっと詳しく知りたいです。

「Vivado」では、ハードウェア記述言語を使って設計を記述し、『FPGA』にその設計を書き込むまでの一連の作業を幅広くサポートしています。『FPGA』が想定通りに動作するように、設定ファイルや回路構成を作り込むことができるんです。この設計記述の工程は、この部分がRTLコーディングと呼ばれています。ここで論理回路設計をしっかり行うことが、『FPGA』での最適な動作に繋がります。

なるほど。

それでは後はこの流れで、ひたすら設計していくだけですね。

でも実際にはどんなポイントに気をつけながらやっていくと良いのでしょう?

それでは後はこの流れで、ひたすら設計していくだけですね。

でも実際にはどんなポイントに気をつけながらやっていくと良いのでしょう?

そう。注意しないといけない落とし穴もあるんです。

それがタイミングです。タイミング問題をうまく処理しないと、設計通りに動かない可能性が出てくるのです。システム全体の動作を考慮して正確に調整することがとても重要です。

それがタイミングです。タイミング問題をうまく処理しないと、設計通りに動かない可能性が出てくるのです。システム全体の動作を考慮して正確に調整することがとても重要です。

検証とは?

タイミング?

タイミングって具体的に何のタイミングですか?

どの部分で影響してくるんでしょうか?

タイミングって具体的に何のタイミングですか?

どの部分で影響してくるんでしょうか?

信号を送受信するときのタイミングのことです。CPUやGPU、そして『FPGA』にはクロック周波数というのがあって、これはデバイスがどれくらいの速さで動作するかを決める指標です。このクロック周波数に合わせて信号が適切に送受信されるようにタイミングを調整しないと、誤動作やデータの不整合が起きてしまうんですよ。

クロック周波数に適したタイミングで動かさないと、『FPGA』は正しく動作しないということですか?

そうです。クロック周波数に合っていないと、適切なタイミングでデータの受け渡しができなくなります。それがいわゆるタイミングエラーというもので、さまざまな種類のエラーにつながります。このため、設計後のテストで気づいた場合には特に手間がかかり、開発者を大いに悩ませる原因になるんですよ。

社内でもタイミングの問題をよく耳にしますね。

エンジニアの皆さんが奮闘しているのも、日々見て実感しています。

エンジニアの皆さんが奮闘しているのも、日々見て実感しています。

タイミングエラーの原因の1つとして異なるクロックで動作する回路間のデータ送受信があります。異なるクロックで動作する回路と回路の接続部分を検証するクロック・ドメイン・クロッシング(CDC)検証を行って問題ないか確認します。

その後、シミュレーションを行い、回路として意図した仕様通りの動作をするか確認します。

そして論理合成を行い、今度は物理的な回路の配置配線によるタイミングエラーがないかを確認するんです。

他にも、ピン配置の制約やタイミング、その他の問題点がないかをしっかりチェックするんですよね。もし問題が見つかれば、その都度修正を行って、再度チェックし直すという流れですよね。このプロセスのおかげで、最終的な設計の信頼性が高まるんですね。

その通りです。この一連のプロセスを確実に実施することによって、ようやく『FPGA』の論理回路設計が完成するのです。このプロセスによって、堅牢で信頼性の高い設計を実現しています!

ふむふむ…。ありがとうございます!これで、『FPGA』の設計開発の一連の流れがよくわかりました。

僕なら、壁にぶつかってお手上げです。

僕なら、壁にぶつかってお手上げです。

実は『FPGA』設計に悩んでいる会社さんが少なくありません。私たちは、FPGAデザインサービスに対して強みを持っていますが、これだけではありません。

と言いますと?

RTLによるコーディング設計だけでなく、私たちは大規模で複雑な回路設計にも対応するために、高位合成設計も行っています。これは、より高い抽象度から設計を進める手法です。また、高位合成・高位検証の統合環境であるシーメンスEDA社のCatapultを用いた設計開発も取り入れ、等価性検証まで実施できます。これにより設計の精度と効率が大幅に向上しています。

あと、先日「RTL Valid™」というサービスをスタートしました。フフフ、紹介する隙を伺っていたんですよ。待っていました、この瞬間を…!

びっくりした、隙あらば宣伝しにくるんですから…。

それで、「RTL Valid™」ってなんですか?初耳です。。。

それで、「RTL Valid™」ってなんですか?初耳です。。。

お客様のRTLで設計したコードを分析・検証サービスです。回路設計が大規模で複雑になると、当然、検証も難しくなります。ミスやエラーを見逃すと、後々に大きな手戻りになってしまいます。

そこで「RTL Valid™」の出番というわけですね!

そうです。たとえば、コードの文法チェックや潜在的な問題の検出、クロックドメイン間の同期がとれているかといった検証などを行います。

今紹介した検証項目はほんの一部です。高品質を目指すべく、様々な検証を行います。問題が早めにわかれば、手戻りが少なくなります。それにかかる時間を抑えることができます!

当社が長年培ってきたFPGA開発経験と技術で、お客様のFPGA開発をガッチリサポートします!

詳しくは下記ページをご覧ください!

詳しくは下記ページをご覧ください!

次回のブログ更新は3月を予定しています。

お楽しみに!

お楽しみに!

- ※記載されている会社名、製品名は、各社の商標または登録商標です。

- ※ここに記載されている仕様、デザインなどは予告なしに変更する場合があります。