Tech Blog

高位合成・高位検証 統合環境を使ったFPGA開発の効果を検証してみた!

小野です!

よろしくお願いします!!

よろしくお願いします!!

こんにちは、小野です。

今回はOKIアイディエスが取り組んでいるFPGA設計の手法の1つである高位合成・高位検証についてお話したいと思います。

OKIアイディエスでは、3月14日に「高位合成・高位検証セミナー第4弾 -多様化・複雑化するニーズに対応!FPGA開発の新パラダイム- 開発メンバーによる統合環境ツール活用事例ご紹介」と題してWebセミナーを開催しました。

近年、アルゴリズムなどの実現手段の1つとしてFPGAの採用が増えています。FPGAの開発はハードウェア言語の記述による論理回路作成、すなわちRTL(Register Transfer Level)設計によって行われます。アルゴリズムが多様化するにつれて、FPGAやASICの論理回路は複雑化、大規模化しており、開発期間も長期化しています。また、従来のIPでは開発における要求仕様を満たせないケースが出てきており、高位合成を活用したFPGA開発の関心が高まっています。

そこで解決策の1つとしてあげられる“高位合成”・“高位検証”によるFPGA開発と、OKIアイディエスが導入している高位合成・高位検証 統合環境による設計開発の事例は多くのセミナー参加者にご興味を持っていただきました。

高位合成・高位検証 統合環境の効果

これだけ注目されているネタを、ブログでも取り上げない理由がありません。渉さん、今日はよろしくお願いします!

久しぶりの登場だな!

みんなに忘れ去られないように頑張らないとな!

みんなに忘れ去られないように頑張らないとな!

ですね!早速ですが、去年の10月ブログでも高位合成・高位検証を取り上げました。この時も統合環境まで解説してもらいましたね。

前回ブログではRTL記述設計/高位合成/統合環境の3つの開発手法を紹介していただきました。統合環境を使う手法は他の2つに比べて、本当にコード量や実行時間などで差が出るのか、同じ処理を3つそれぞれの手法で作って比較したいです。

よし、ちょいと待ってて。

よし、昔RTL設計で開発したアナログ信号の処理モジュールを高位合成/統合環境でそれぞれ再設計してきたぞ。これで3種類の開発手法を比較してみるぞ。

早すぎですよ!どんなモジュールを作成したんですか?

窓処理モジュールというものだ。アナログ信号を処理するとき折り返し雑音などの影響を抑えてくれる効果があるんだ。

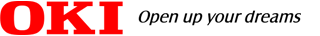

入力は図中の左の演算されるデータと演算係数、バイパスのon/offの3つですね。

その通り。簡単にまとめるとこんな感じです

- データと係数は固定小数点での入力になり、出力は演算結果を浮動小数点で出力する

- バイパス機能を保有しており、演算処理する/しないを入力のバイパスon/offで制御する

- RTL開発でのブロック構成としては図の8個のブロックから構成

- IQデータ分離

- 固定小数を浮動小数へ変換する処理(2ブロック)

- 窓関数処理バイパス切替

- 演算処理(2ブロック)

- バイパス切替出力データ選択

- 演算結果IQデータ結合

RTL/高位合成/統合環境による比較検証ではそれぞれどんなツールを使ったんですか?

RTL設計にはVivado(AMD社製)、高位合成設計にはVitis HLS(AMD社製)、そして高位合成高位検証の統合設計環境のCatapult(シーメンスEDA社製)だ。

いきなりですが結果を見ていきましょう!

本当にいきなりだ….。

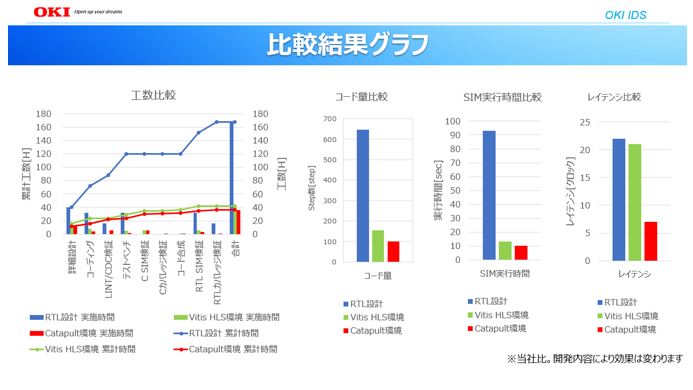

それぞれの設計での、工数、コード量、シミュレーション実行時間、レイテンシを比較したグラフだよ。青色がRTL設計、緑色が”高位合成”設計、赤色が統合環境設計の結果だ。

RTL設計に対し、高位合成設計/統合環境設計は工数、コード量、シミュレーション実行時間共に、大幅な削減効果のあることが分かります。

コード量比較のグラフを見ると「高位合成設計」と「統合環境設計」の記述量にも50ステップ近い差が現れたんだ。不思議に思わない?

本当にこんなに変わるんですか?両方とも同じ機能なんですよね?

ということで作成したものを詳しく調べたところ、特にパイプライン化の指定部分で2つに大きな差があることがわかったんだ。高位合成(Vitis HLS)は、パイプライン化を意識した複数の関数へ処理を分割する記述を行ったんだ。

それに対して統合環境設計(Catapult)では違う指定をしていたんですよね。どう違ったのかが気になります。

統合環境(Catapult)は、記述ではなくて、パイプライン化をツール画面上で指定していたんだ。そして、ステップ数は高位合成(Vitis HLS)は、86ステップ、統合環境(Catapult)は、39ステップになったんだ

この差によって開発期間短縮の効果があったと考えられますね。レイテンシも大きな違いが出ていますよね。

高位合成(Vitis HLS)は、21クロック、統合環境(Catapult)は、7クロックという結果になったよ。高位合成(Vitis HLS)のレイテンシは、RTL設計と同等だったよ。でも、統合環境(Catapult)は、他の2つの手法よりも、レイテンシが低い結果になったんだ。

レイテンシも抑えられている…?

同じ機能のものを開発したんですよね?改善した結果になっていますけど本当に同一機能になっているんですか?

同じ機能のものを開発したんですよね?改善した結果になっていますけど本当に同一機能になっているんですか?

3つ作ったモジュールをそれぞれ入れ替えて実機確認をしたら正常に動いたよ。同じ機能なら同じ処理をしてくれるはずだから、同一の機能になってるんだ。

なら、なぜレイテンシまで変わってしまうんですか?

そこを追加で検証することにします!設計者の意図していない論理回路ができてしまったとしたらそれはそれで問題になるからね。

同機能RTLの単ブロック/複数ブロックでの比較検証結果

さっきのモジュールの窓関数を、ブロック構成1個の場合と8個の場合で検証してきたぞ。

予想してなかった論理回路を構築していたと思ったけど、これは統合環境(Catapult)の狙い通りなのかもしれない。

予想してなかった論理回路を構築していたと思ったけど、これは統合環境(Catapult)の狙い通りなのかもしれない。

設計者が意図した通りの動きをするようコードを合成しつつ、内部の処理を自動で最適化していることも考えられます。

ブロック構成を単数と複数の違いのイメージとしてはこんな感じ。複数ブロックに分けると隙間時間ができるけど、単ブロックならその隙間時間をなくすようにして合成するんじゃないかって予想だ。

処理の順番を入れ替えて、より短時間で終わるようにすることでレイテンシが抑えられるということですね。

気になる結果は…?

気になる結果は…?

複数ブロックの場合は12クロック、単ブロックの場合は7クロック!本当に短時間で終わるようになっていたんだ。

ということは、単ブロックは複数ブロックの1.7倍くらい早く処理が終わるということですよ!

詳細はこんな感じだよ。

| 複数ブロック | 単数ブロック |

|---|---|

|

|

同一の機能でもモジュールの構成によって、処理速度が異なることがわかる。人の手で処理の順番を調整したりすることはあるけど最適化の精度は統合環境(Catapult)の方が上だったね。

それは大きな収穫ですね。よりレイテンシを抑えられるならありがたいですよね。やっぱり高位合成は奥が深いですね!

統合環境を活用した、FPGA設計開発は、まだまだ開拓の余地がありそうだ。もっともっと高度な設計ができるように今後も統合環境(Catapult)を使ったFPGA開発に力をいれていくぞ!前進あるのみだ!

高位合成、高位検証の質問に答えるコーナー

高位合成、高位検証に関する疑問や質問に答えていくぞ!

唐突に始まったコーナー。

確かに高位合成・高位検証 統合環境に関する疑問や質問を多くいただきますからね。ボクが質問を読み上げていきます。

確かに高位合成・高位検証 統合環境に関する疑問や質問を多くいただきますからね。ボクが質問を読み上げていきます。

それでは最初の質問です。

『コード合成工程において、生成指定の処理時間の指定とは、何クロックで処理を終えてくださいといった指定ができるということでしょうか?』

『コード合成工程において、生成指定の処理時間の指定とは、何クロックで処理を終えてくださいといった指定ができるということでしょうか?』

残念ながらレイテンシは指定できません。

指定できるのは、以下の2つです。

・スループット:ツール上、又は、C コードの pragma で指定することが可能。

・リソース:BRAM/URAM/ レジスタの、どれを使用するか指定することが可能。

指定できるのは、以下の2つです。

・スループット:ツール上、又は、C コードの pragma で指定することが可能。

・リソース:BRAM/URAM/ レジスタの、どれを使用するか指定することが可能。

次の質問です。

『高位合成は RTL 設計に比べて、回路規模が大きくなるイメージがあります。実際に回路規模は大きくならなかったのでしょうか?』

『高位合成は RTL 設計に比べて、回路規模が大きくなるイメージがあります。実際に回路規模は大きくならなかったのでしょうか?』

高位合成で作成した回路はそこまで大規模にはなりません。今までの設計開発ではRTLと比較しても大きく変化はしませんでした。設計時にBRAM使用量の見積を行いましたが、見積から大きくはずれることはなかったです。

次の質問です。

『高位合成を使うことで効果が出やすい処理、出にくい処理などはあるのでしょうか?』

『高位合成を使うことで効果が出やすい処理、出にくい処理などはあるのでしょうか?』

画像、信号処理などパイプライン処理が必要なものや並列処理が明確なアルゴリズムは効果が期待できます!

逆にSPI, GPIO など、クロック単位での動作設計が前提で、 FPGA 外部とやり取りを行うもの、PCIeなどIPが充実している場合は効果が出にくいです。

逆にSPI, GPIO など、クロック単位での動作設計が前提で、 FPGA 外部とやり取りを行うもの、PCIeなどIPが充実している場合は効果が出にくいです。

開発開始前の見積段階で高位合成の効果を確認します。

効果が小さい場合は従来のRTLで設計します。

効果が小さい場合は従来のRTLで設計します。

次の質問です。

『RTLを考慮した C コードの構文チェックができない場合、 C で記述した動きとRTL での動きが異なるときがあるとのことですが、どのような記述を行うとそのようなことが発生するのでしょうか?』

『RTLを考慮した C コードの構文チェックができない場合、 C で記述した動きとRTL での動きが異なるときがあるとのことですが、どのような記述を行うとそのようなことが発生するのでしょうか?』

Cコードの構文チェックではfor文のループを使うと指摘量が増えました。Cと RTL の Sim で結果が異なるケースとしては、上記のほか、当社での経験上、入力と出力の対応が1:1でないとき (入力は行うが出力しない記述があるときなど)に異なっていました。

どんどん次の質問に行きますよ。

『高位合成ツールはツール依存の部分があると思うのですが、たとえばVitis HLS ⇔ Catapult 等の移植をする場合、簡単にできるものでしょうか?』

『高位合成ツールはツール依存の部分があると思うのですが、たとえばVitis HLS ⇔ Catapult 等の移植をする場合、簡単にできるものでしょうか?』

Vitis HLS ⇔ Catapultの変換難易度は低いという認識です。

ただ、ツールなどで一括変換ができないため、人の手で修正が必要な部分はありました。

ただ、ツールなどで一括変換ができないため、人の手で修正が必要な部分はありました。

それってどんな機能を開発しているときでも

Vitis HLS ⇔ Catapultの変換はできるんですか?

Vitis HLS ⇔ Catapultの変換はできるんですか?

全部簡単に変換できるとは限らないです。ツール固有のライブラリや拡張の使用度合い、対象とするハードウェアアーキテクチャの違いなどに強く依存すると考えられます、是非ご相談いただければと思います。

ありがとうございます。結構いっぱい答えましたね。まだまだ質問はありますが…。

今回はここまで!

次回はいただいた質問1000個にズバッと答えていきます!!

次回はいただいた質問1000個にズバッと答えていきます!!

あ、QA終わったら、口調が元に戻った!頑張ってたのね。

まるで1000本ノックだ・・・昭和ですよ(笑)

でも、それはさすがに厳しいです、勘弁して…。

まるで1000本ノックだ・・・昭和ですよ(笑)

でも、それはさすがに厳しいです、勘弁して…。

さすがに冗談で~す。

でも、当ブログを読んでくださっている方で、FPGAの開発でもしお悩みやお困りごとなどがあれば是非当社へご相談ください!

でも、当ブログを読んでくださっている方で、FPGAの開発でもしお悩みやお困りごとなどがあれば是非当社へご相談ください!

そういえば・・・

先日のセミナーのタイトルに「FPGA開発の新パラダイム」って書いてありましたね。新パラダイムって何だったんですか?危うく聞き逃すところでしたよ!

ここは私の出番ですね、お任せください!

待ってました!(ほんとに出たがりだな…)

ソフトウェア開発が登場した初期のころは、機械語やアセンブリ言語といった抽象度の低い言語を使って、開発者がプログラミングしていました。

今ではC言語やJavaとかPythonがありますよね

今でもD言語やGoといった新しい言語も登場していますよ。こういった高級言語は、さっきの低級言語より抽象度が高く、生産性UPなど多くのメリットをもたらしました。

ソフトウェア開発の歴史がFPGA開発の歴史に関係しているんですか?

ソフトウェア開発が発展するとともに、FPGAやハードウェアの開発も発展してきた経緯があるんです。

すでにRTL記述設計は、使用する言語の抽象度が低く、どう頑張っても生産性を上げるにはすでに限界です。

すでにRTL記述設計は、使用する言語の抽象度が低く、どう頑張っても生産性を上げるにはすでに限界です。

そこで高位合成が登場しました。抽象度が高い言語を使うので生産性UPにつながったんですよね。

高位合成技術やツールも時間が経つにつれて進化しました。

しかし、C言語のように広く普及はしませんでした…。

しかし、C言語のように広く普及はしませんでした…。

C言語やPythonを使ったソフトウェア開発は今となっては普通ですよね。このような高級言語を使えるのに、なぜ高位合成は普及しなかったんでしょう?

等価性検証がツール上で実施できなかったことが要因でしょう。「C言語で動いたのに、高位合成後に動かない…」なんてことがあると、どこが悪かったのか調べて修正する必要があります。

そこがずっとネックになってました。

が、統合環境(Catapult)を導入したことで、当社では等価性検証がツール上でできるようになりました。

この開発手法が近い将来スタンダードになるはずです。これこそがまさにパラダイムシフトというわけです!

が、統合環境(Catapult)を導入したことで、当社では等価性検証がツール上でできるようになりました。

この開発手法が近い将来スタンダードになるはずです。これこそがまさにパラダイムシフトというわけです!

そういう意味だったんですね!

すでに、より高度なハードウェア開発が求められています。そんな中、OKIアイディエスは、そんなハードウェア開発にもどんどんチャレンジしていますから…。

すでに、より高度なハードウェア開発が求められています。そんな中、OKIアイディエスは、そんなハードウェア開発にもどんどんチャレンジしていますから…。

どんなハードウェア開発も、どんと来い!と構えています。

それにしてもパラダイムシフトっていう言葉、かっこよくてナウい響きですね…。2024年度もスタートしましたし、私もクールかつスマートにパラダイムシフトしますよ…!

それにしてもパラダイムシフトっていう言葉、かっこよくてナウい響きですね…。2024年度もスタートしましたし、私もクールかつスマートにパラダイムシフトしますよ…!

ナウいってなんですか…?

(「パラダイムシフト」って、「考え方や認識が劇的に変化する」という意味では…。多分言葉の使い方間違っています…。)

(「パラダイムシフト」って、「考え方や認識が劇的に変化する」という意味では…。多分言葉の使い方間違っています…。)

次回のブログ更新は5月を予定しています。

お楽しみに!

お楽しみに!

- お問い合わせ

- お問い合わせフォームはこちら

- ※記載されている会社名、製品名は、各社の商標または登録商標です。

- ※ここに記載されている仕様、デザインなどは予告なしに変更する場合があります。