- Home

- 製品トップ

- GigE Vision®ソリューション

- GigE Vision® V2.0 Rx FPGA IPコア

製品

AMD FPGA用 GigE Vision® V2.0 Rx FPGA IPコア

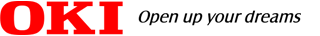

Zynq UltraScale+™ MPSoCへの受信側GigE Vision® プロトコルかつGENiCAM対応により、組込み機器へGigE Visionカメラ画像受信を収容することが 適応型SoC 1chipで実現可能 !!なおかつ、高速で信頼性の高い映像伝送を可能にします。

特徴

- GigE Vision® V2.0プロトコルによるイーサネット映像リアルタイム受信が可能

- GigE Vision® V2.0の標準機能の他、Pending Acknowledge、Scheduled Action Command、All-in Transmission Mode Packetなどに対応

- 1G/10Gbpsのイーサネットに対応。最大10Gbpsの帯域をフルに活用した映像伝送を実現

- OKIアイディエス製 UDPオフローディングエンジン(UoE)搭載。GigE Vision®プロトコルの制御は、全てFPGA内部(MicroBlaze™)で処理。ハードエンジン(UoE)+GigE Vision®スタックにより高速映像受信を実現

- FPGAは、Zynq UltraScale+ MPSoCに対応※

- AIA's Machine Vision協会に正規認定されているFPGA/SoCソリューション

- 複数のGiGE Vision®カメラ収容に対応

- ※ FPGAデバイスにより、対応可能な伝送速度は異なります。また、記載した以外のFPGAにも対応可能ですので、ご相談ください。

システム構成例

ハードエンジン(UoE) + GigE Vision®スタックにより高速映像受信可能。

組込み機器へのGigE Vision®対応を 適応型SoC 1Chipで実現!

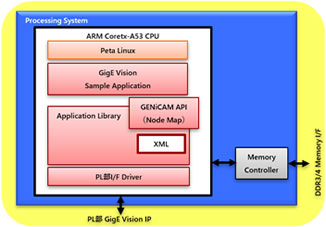

GigE Vision®受信(GENiCAM) ソリューション構造図

Zynq UltraScale+ MPSoC PS部構成図

- カメラ制御は、Camera Description File (XML)を解釈したGenICam API (Node Map)を経由して制御可能

- カメラから送られる映像Streamは、PL部のGVSP UDPオフロードエンジンが素早く切り離すのでStreamの受信率を向上可能

- 切り離された映像StreamはARMを介さず、直接Video Frame Bufferへ転送するのでCPU負荷を低減

- ARMのOSはAMD標準のPeta Linuxを採用

- OKIアイディエスは、Peta Linuxの推奨デザインサービスパートナーであり、サポート面も安心

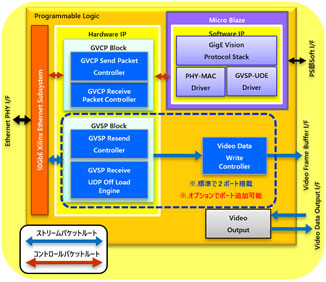

Zynq UltraScale+ MPSoC PL部構成図

- OKIアイディエス製“GigE Vision UDP Offloading Engine“を搭載し、GigE Vision®プロトコルパケットの高速映像受信を実現

- MicroBlaze™上 に”GigE Vision®プロトコルスタック”、”MACドライバー”、”GV-UOEドライバー”を実装し、全てのGigE VisionプロトコルをPL部で終端

- GigE Vision™プロトコルにより、パケットロストの欠損データ補完を行い、高安定性を実現

- EMACには、AMD製 1G/10G/25G Ethernet Subsystem を使用し、データリンク層の制御を実施

提供製品

- FPGAデザインに必要となるIP+リファレンスデザイン+PS部/PL部の全ての開発環境とマニュアルをご提供します。

サポート体制

- 国内製IPによる完全日本語サポート(電話/メール/各種マニュアル全て)

- 技術サポートは全て当社技術者が直接対応いたします。

- ※記載されている会社名、製品名は、各社の商標または登録商標です。

- ※ここに記載されている仕様、デザインなどは予告なしに変更する場合があります。