Tech Blog

実は色々やってます!OKIアイディエスの電子回路設計

小野です!

よろしくお願いします!!

よろしくお願いします!!

こんにちは、小野です。

今回はOKIアイディエスの電子回路設計技術とシミュレーション技術をご紹介します。

小野くん、今日は昔話をしましょう。

また突然何か始まりましたね。

むかーしむかし、データ伝送の設計をしているおじいさんがいました。1秒間に数バイトの伝送速度が求められていたそうな。

ずいぶんとおっそいですね。

しかし、近年、データセンターやAIシステム、ネットワークインフラ分野を中心に「もっと速く」「もっと大容量に」というデータ伝送のニーズが高まっています。PCI Express 7.0やUSB4も登場し、1秒間に数十ギガバイト~数百ギガバイトものデータがやり取りされる時代になりました。

あれ、急に現代に?昔話が一瞬で終わりましたよ…。

今日はデータ伝送技術の歴史について語ろうとしていたのですが…。やはりおじさんの話は長いし、遅いって言われますし。巻きすぎたかな?

巻きすぎです。「遅い」というのは、伝送速度の話です!

まあまあ。当ブログではこれまでに、「iGiGE」に「iTOE」、「iDMAC」と多彩な高速データ伝送技術を紹介してきました。それから、「RTL Valid」というFPGA開発におけるRTLコード検証サービスも。

たしかに。今年は我が社のソリューションや新しいサービスを色々紹介してきましたね。ソフトとかFPGA開発のサービスがメインでしたが、実は電子回路設計や機構設計もやっていますよね。

もちろんやっていますよ。電子回路設計や機構設計ができる技術者もいますからね。OKIアイディエスの設計は、大きく分けると、「ソフトウェア設計」、「FPGA設計」、「電子回路設計」、「機構設計」、「実装設計」の5つの分野で構成されています。

これまでのブログでは、電子回路設計や機構設計は取り上げてきませんでした。今回のブログでは、「電子回路設計」の解説をお願いします!

分かりました。それでは、OKIアイディエスの「電子回路設計」を解説していきましょう。

「電子回路設計」と「基板設計」の違い

よく「電子回路設計」って聞くんですけど、「基板設計」とは何か違いってあるんですか?

実は、区別して使っています。「電子回路設計」とは「要求された仕様や性能を満足するために電子部品の接続を設計すること」です。回路の動作や特性を考える工程ですね。

へぇ~。対して、「基板設計」はどうなんでしょうか?

一方、「基板設計」とは、「電子回路設計で作った接続構成をプリント基板に落とし込み、パターンを設計すること」です。求められる基板のサイズや形状に合わせて、ガーバーデータを作成しています。

「電子回路設計」→「基板設計」というのが大まかな流れですね。

That’s right! 「電子回路設計」、「基板設計」を経て、電子部品が実装された基板が製造されます。その後、完成した基板が基板仕様どおりに動くかを検査するんです。

言っておきますが、基板仕様書を作らずに回路図を作ってはいけませんからね。

言っておきますが、基板仕様書を作らずに回路図を作ってはいけませんからね。

基板仕様書の作成、大事なポイントですね。

そうです。次は電子回路設計のポイントへlet’s go!

高速信号伝送 ~伝送路長と波形減衰の関係~

電子回路のデータのやりとりは「0」と「1」の信号のやりとりです。データの高速伝送では信号が高速かつ大量に送られます。しかし、基板に求められる仕様や部品点数が多くなると、問題が出てきます。たとえば…。

- 配線経路の複雑化(信号間の干渉)

- クロストークの増加(ノイズの発生)

- 発熱量の増加

- 部品の実装密度の制約

そして、高速でデータ伝送しようとして伝送速度を上げると周波数が高くなります。高周波になると信号の減衰が発生してしまうんです。特に部品同士の伝送路、つまり配線が長いと特に発生しやすい問題です。

信号が減衰?よく「信号の波形が~」とか、開発部から聞きますけれど、それと関係ありそうですね。高周波って減衰しやすい理由があるんですか?

たとえば、基板配線を流れる信号は高周波になるほど、配線の表面近くだけを通るようになります。つまり実質的な電流の通り道が少なくなり、抵抗が大きくなって損失が大きくなるんです。

そんな特性があるんですね。ってことは信号が減衰、すなわち損失が大きくなると、信号の正確性が失われてしまいますよ。

損失が大きくなると、「0」「1」の区別がつきづらくなりビットエラーの原因になります。つまり、データ伝送が正しく行われないという事態になるわけです。

周波数を下げると、今度は速度低下になっていまいますね。このバランスが難しそうです。じゃあ、部品同士の伝送路を短くすればいいんじゃ?

誰でも最初に思いつきそうなアイデアですが、基板サイズ・レイアウト制約・設計規格・熱・ノイズ・配置の自由度の都合でどうしても長い信号経路が必要だったり、放熱やノイズといったことを考慮して配置しないといけない制約もあり、そう簡単に実現できるものではないんです。

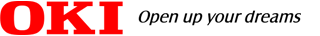

これは挿入損失(インサーション・ロス)と言って、伝送路の損失を表しているんですけど、周波数が高くなるにつれて、信号が小さくなっています。

減衰が発生していることがわかりますね。ちなみに、最近の基板に対する要求ってどのようなものが出てきているんですか?

たとえば、PCI Expressの規格では、PCI Express 6.0から、PAM4シグナリング技術が導入されます。従来は2つの振幅レベルの信号を使っていました(NRZ方式)が、PAM4では4つの異なる信号を使うことで1つのシンボルで2bit分の情報を送る技術です。同じ帯域幅でも、従来よりもずっと高い伝送速度を実現します。ただし、ノイズに弱く、信号品質の管理が難しくなっています。

1つのシンボルで2bit分ということは単純に今よりも伝達できる情報量が2倍になる…そう考えるとすごいですね。

さらには身近なUSBにも新しい規格が登場しました。USB3.0の最大伝送速度は5~20Gbpsですが、次世代のUSB4 ver2.0では、最大伝送速度は80Gbpsを実現しました。

身近な規格がどんどん進化しているんですね。今後色々な開発で採用されていくと思いますけれど、つまり、先ほどの信号の減衰やノイズ、発熱対策等が必要となりそうです。こうして、基板への要求がどんどん高くなっているんですよね。

開発も高度化が進んでいますが、製造した基板の評価も難しくなっているという開発現場の声もあります。たとえば、「高密度化によりプローブをあてることが困難となり測定ができない」、「高速化により信号の伝送速度がオシロスコープの帯域を超え、測定できない」など。

基板が多層になっていることも多いですよね。部品が基板の層の中にあるとプローブを当てて評価なんてできません。しかし、きちんと見ておかないと後から大変なことになりますよ。

実際に、基板設計して実物ができ上がったらいざ動作確認!DDRが動作しません!!ということも昔はありました。調査すると、信号品質に問題が…。

実機では原因の特定も難しくなるでしょうし、基板の作り直しになると開発スケジュールにも影響が…。うーん、難しくなってきた…。設計するにも実機評価するにも、工夫が必要だと思います。OKIアイディエスではどんな取り組みをしているのですか?

そこで、事前検証を行います。つまりシミュレーションにより信号の「高速化」、基板の「高密度化」による問題点を事前に見つけることが重要なんです!

ここでもシミュレーション!事前に理論上で確認し、不具合の原因となるものを早期発見、修正することができますが、どんなシミュレーションするんですか?

たとえばSI(Signal Integrity)、PI(Power Integrity)、EMC(放射ノイズ)などがあります。こういったシミュレーションを基板設計から基板製造に移行する前に実施するのです。基板製造後に不具合が発覚したら、不具合修正して基板を再び製造しなければなりませんからね。

ソフトウェアのように修正がすぐ反映できるわけじゃないですもんね。製造には時間とコストがかかりますから、インパクトがかなり大きいですよ。OKIアイディエスは電子回路設計をメインで行っていますが、基板設計とシミュレーションも実施できるんですか?

基板設計とシミュレーションは、生板製造を行うOKIグループの関連会社であるOKIサーキットテクノロジーに依頼しています。

実際の設計事例

OKIアイディエスとOKIサーキットテクノロジーが一体となってワンストップを実現しているんです。ここで、ひとつ実際の設計事例でもご紹介しましょうか。

AMD製FPGA Versal ™ プライムを搭載したPCI Expressボードの設計です。

AMD製FPGA Versal ™ プライムを搭載したPCI Expressボードの設計です。

Versal ™といえば、AMD製FPGAの中でもハイエンドな性能を持つデバイスですよね。ハイエンドのデバイスを使った電子回路設計、基板設計は大変だったのではないですか?苦労話、ぜひ聞きたいです!

いいですよ。光高速通信やPCI Express Gen4、NVMe SSD、DDR4など、高帯域の通信制御が必要であり、ハイエンドのVersal ™を採用して評価ボードの回路を参考にして設計を行いました。

私も少しだけVersal ™のテクニカルリファレンスマニュアルを見ました。何百ページにもわたる内容を理解するのは非常に難しいですよね。

他にも、電子回路設計の段階で、ピン配置のためにFPGA設計部隊に仮合成をお願いしたり、採用するDDRやフラッシュメモリーがFPGA開発の面で問題ないかを確認したり、ソフトウェア開発の面でデバイスドライバーが提供されるチップを選んだり…。

やることてんこ盛りですね。

デバッグしやすいようLEDやディップスイッチを取り入れたりと、FPGAやソフトウェアの開発コスト、製造コストも意識した設計を行えるのが、OIDSの電子回路設計の特徴なんです。

FPGA設計やソフト設計のことも考慮して、部品やチップ選定したり、構成を考えて、電子回路設計が行われていたんですね、実はあんまり知らなかったです。この事例に限らず、FPGA、ソフト、電子回路設計それぞれが一体となって機能実現に向けて開発を進めているんですね。

特にこの案件では、PCI Express規格のボードサイズの中に16個のDDR4を実装する必要があり、基板表面上は部品でいっぱいだったんです。

基板にびっしり部品があったら、信号配線が大変そうです。単につなげるだけじゃないんですよね?

そこなんですよ。PCI Expressの規格に則り、16GB/sの伝送速度を実現する基板設計とのスムーズな連携が必要になります。その設計ができるのが、OKIサーキットテクノロジーです。

ここで、OKIサーキットテクノロジーが登場するんですね!回路設計データをもとに基板設計を実施してもらうことになりますから、そこで不足や間違いがないようにするのがポイントですよね。あと、基板に落とし込んだ時に、狙い通りの信号伝送にならないってことはないですか?

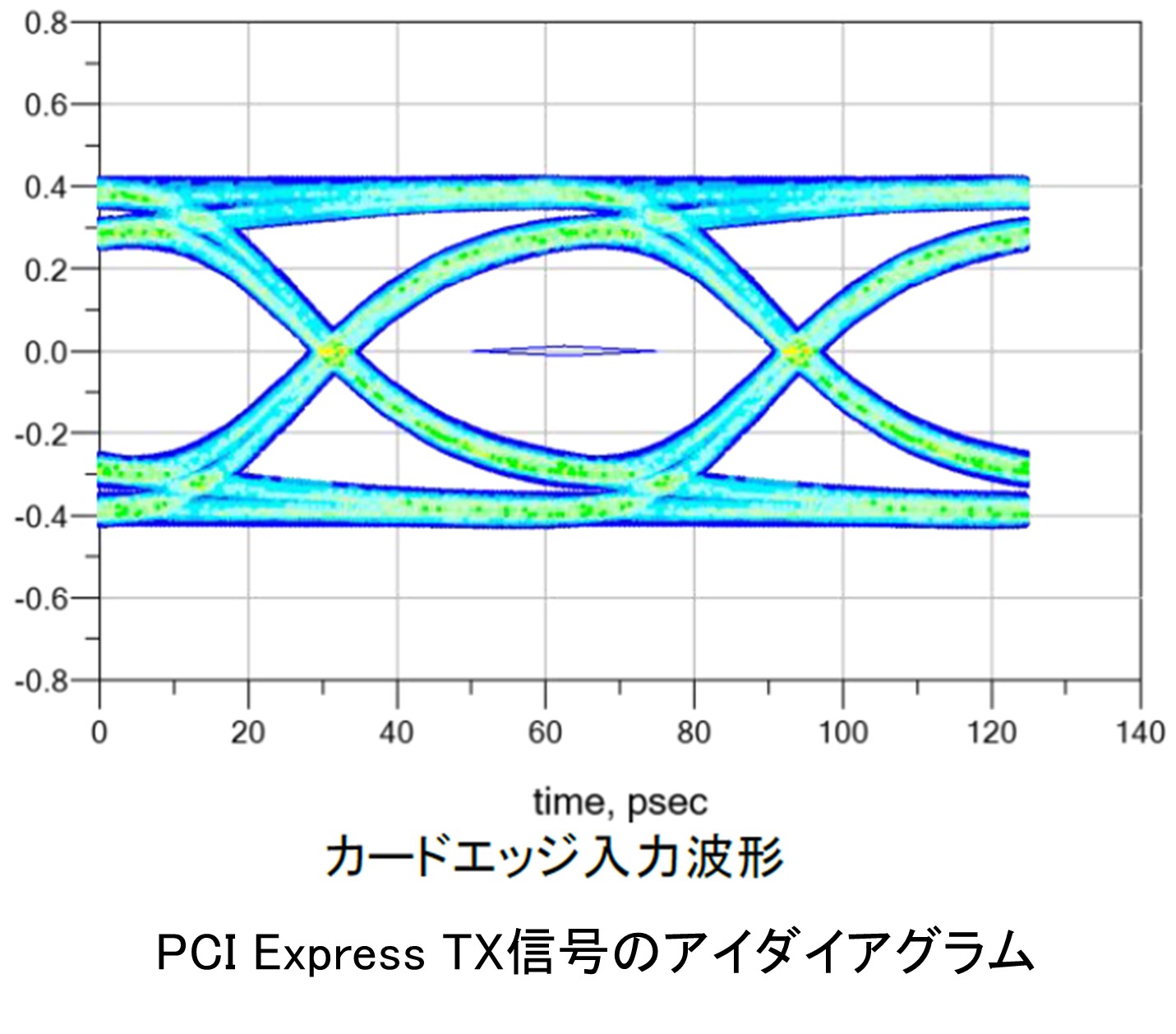

基板設計ができたら、信号品質を確認する必要があります。そこでシミュレーションとして、たとえば下記のようなアイダイアグラム(Eye Diagram)の評価を実施しました。

これは何を評価しているんですか?

システムの物理特性の評価です。信号が伝送中に歪んだりすることがないかを確認する評価になります。図中の中央部分の上下の間隔や、左右の広さを「アイの開口」と言い、これが十分開いていれば、信号が歪むことなく正確に伝送できているということが判断できるんです。

ここで正常だって判断ができれば、「もし動かなかったら…」という不安なく、安心して基板製造に進めますね。

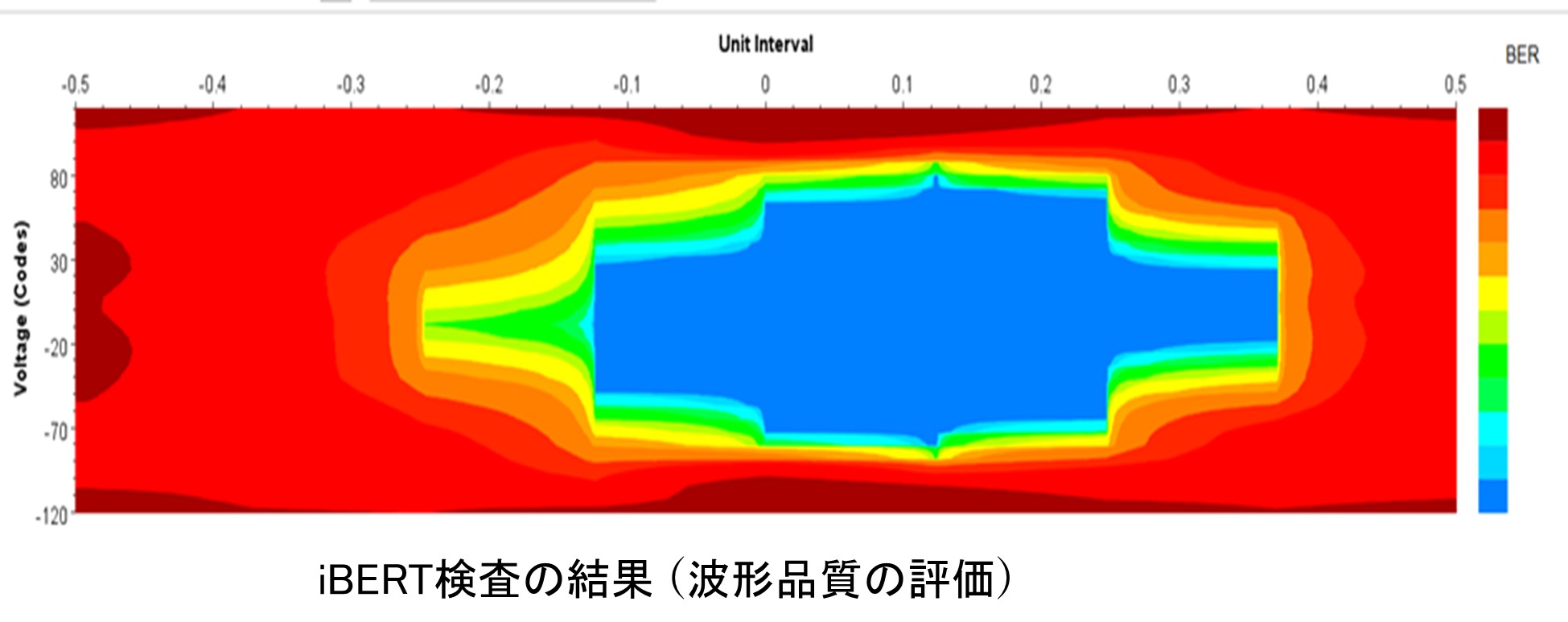

あとは、基板を製造後に出来上がった基板がシミュレーション通りに動作するか、検査を実施します。FPGAの高速シリアルインターフェース(トランシーバ)で伝送される信号の品質評価を確認するiBERTというAMDの高速シリアルインターフェイス評価ツールを使って、トランシーバ機能を確認するんですよ。

先ほどのシミュレーションと同様に上図のアイパターン(Eye Diagram)の中で、信号のアイがどれだけ開いているか=信号がどれだけ明瞭か(マージンがどれだけあるか)を確認するんですね。信号品質の評価方法を理解できました。

わかってもらえましたか。設計段階のシミュレーションと基板製造後の信号品質評価の突合せが重要です。

最後に

OKIアイディエスはAMD社のプレミアパートナーに認定されています。豊富なFPGA・ソフト開発の実績に加え、開発コスト・製造コストを意識した電子回路設計・基板設計に取り組んでいます。

そうですね。これからもOKIグループとしての連携を強化して、さらに品質の高い設計を目指しますよ。使用する基板の伝送モデルをOKIサーキットテクノロジーから提供してもらい、その伝送特性を考慮した電子回路設計を行うことを現在考えています。

基板って特性やクセがあったりしますよね。それをあらかじめ把握しておけば、より質の高い設計ができそうです。

我が社で実施した実機評価結果をOKIサーキットテクノロジーへフィードバックし、シミュレーションと実際の結果とのギャップを埋めることも行っています。

知らないところでそんな取り組みが!どちらも設計の質を大きく向上できそうですね。

ぜひ知ってくださいね。ということで、うまくまとまったかなと思いますので今日はこれまで!小野さん、キリもいいのでこの後飲みにケーションでもどうかな?

すみません!今日は予定がありまして、また今度!(ボスとのジェネレーションギャップは埋まりそうでなかなか埋まらないなぁ。。。)

次回のブログ更新は2026年1月を

予定しています。お楽しみに!

予定しています。お楽しみに!

- ※記載されている会社名、製品名は、各社の商標または登録商標です。

- ※ここに記載されている仕様、デザインなどは予告なしに変更する場合があります。